### Enhancing the MPI Collective Communication Performance utilizing iMEX (intelligent Memory EXpander)

ETRI

Supercomputing System Research Section

August 21, 2024

Hooyoung Ahn

### Contents

- Motivation & Problem Definition

- Project Goals

- Roles of ETRI and OSU

- Our Approach

- Road Map

- Conclusion

## Motivation & Problem Definition (1/3)

- Large-scale data-intensive applications in HPC and AI require distributed processing in a multi-node environment

- At this time, there is large and complex communication between nodes, and providing sufficient memory capacity for these applications is one of the necessary conditions for improving performance.

- For example, LLM applications perform distributed training because the huge size of models and training data [1]

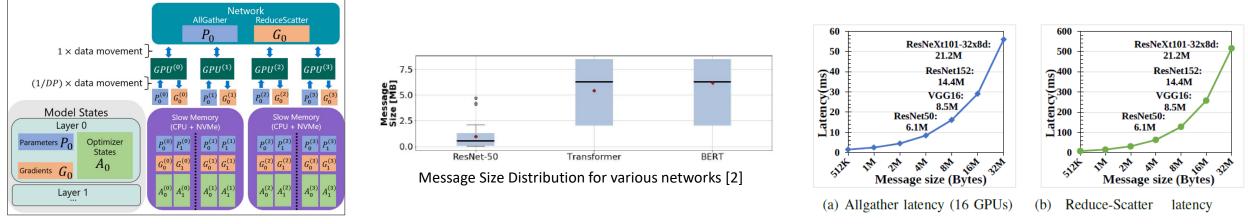

- AllGather and ReduceScatter are used as the main collective communications

- As the data and model size increases, the collective communication message size increases [2]

- However, AllGather and ReduceScatter have problems with increased latency for large messages [3]

Message sizes of Allgather and Reduce-Scatter in PyTorch FSDP Training on 16 GPUs [3]

A snapshot of ZeRO-Infinity training [1]

### Motivation & Problem Definition (2/3)

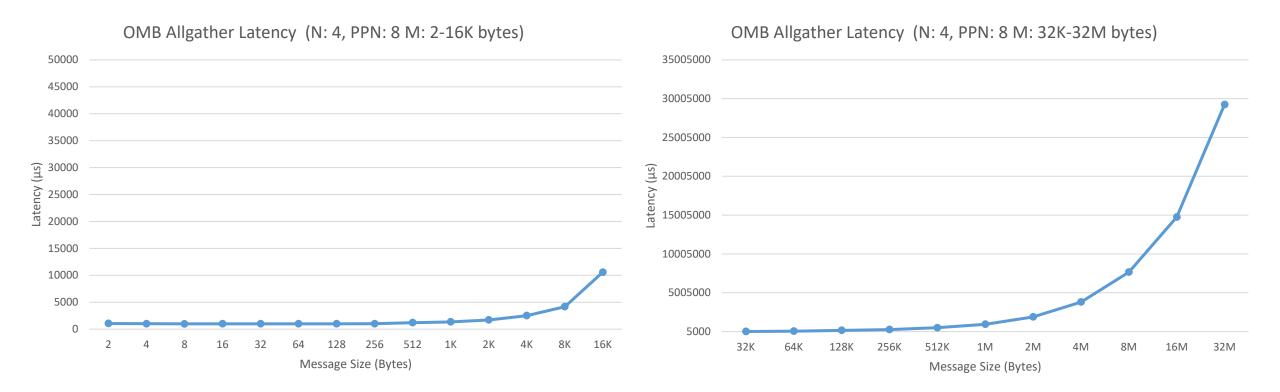

• As the message size increases, communication latency of traditional allgather also increases

Experimental Results on ETRI's QEMU-based 4 Computing Nodes

## Motivation & Problem Definition (3/3)

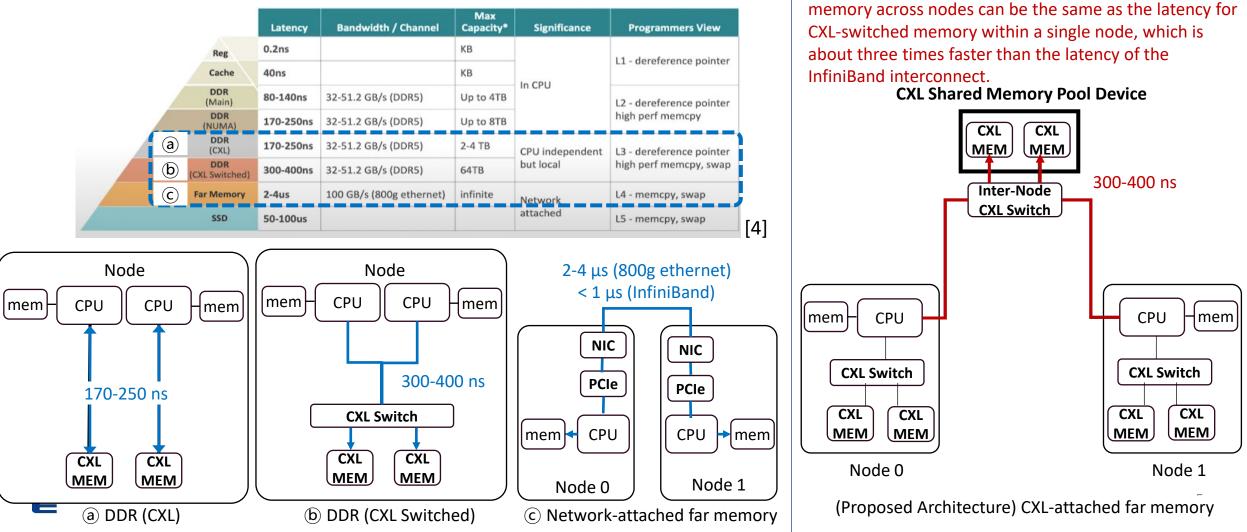

We believed that we could address this issue by using the CXL interconnect and the CXL shared memory pool device in a single rack, which provide faster communication latency compared to traditional multi-node interconnects using Ethernet or InfiniBand.

### **Project Goals**

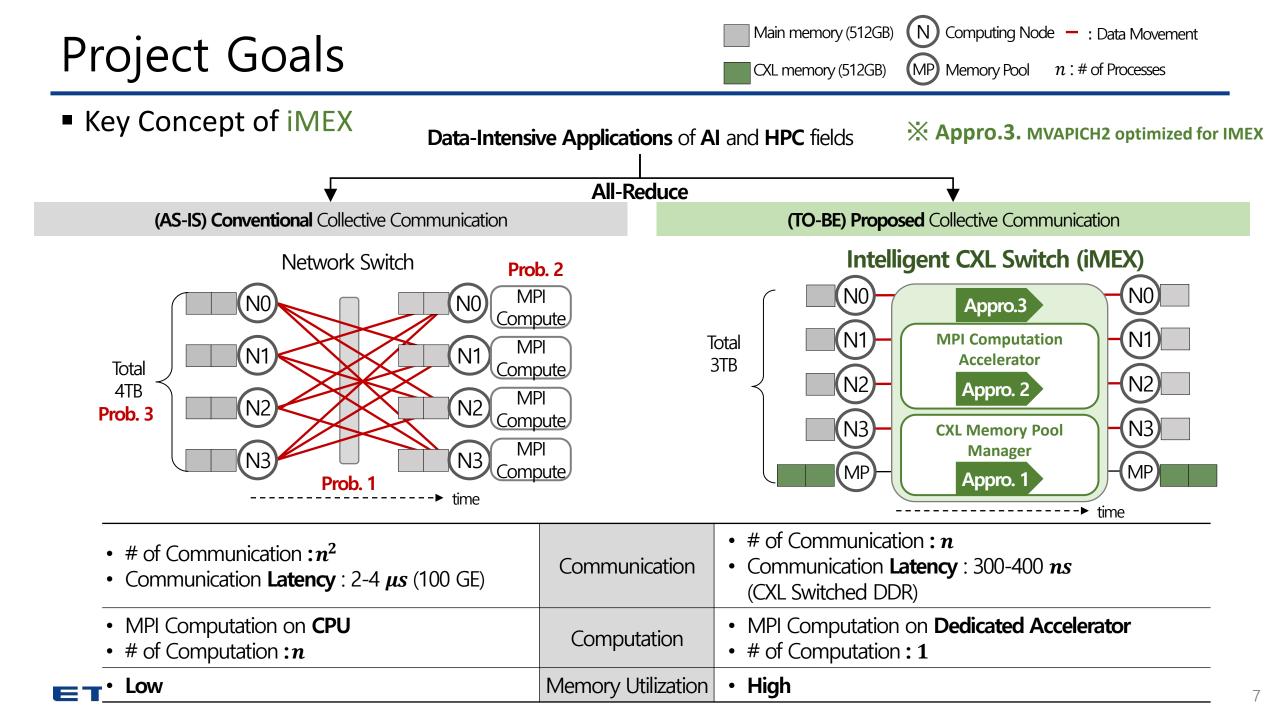

- The goal of this study is to enhance the MPI Inter-Node collective communication performance in a multi-node environment connected by CXL

- Two Specific Goals

- Goal 1. Utilizing the CXL shared memory pool for collective communication

→ 1<sup>st</sup> phase: Sept. 2023 Aug. 2024

• Goal 2. Utilizing the intelligent CXL switch for collective communication

$\rightarrow$  2<sup>nd</sup> phase: Sept. 2024 - Aug. 2025

→ To achieve above goals, we proposed iMEX (intelligent Memory EXpander)

|      | Research<br>Area | Focus                                              |   | Research Item                                                                                                                                         |

|------|------------------|----------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSU  | Goal 1           | Beyond Rack-<br>Scale CXL<br>Memory Pool           | 1 | Improving collective communication performance by utilizing the <b>beyond rack scale CXL</b><br>memory pool device                                    |

|      |                  |                                                    | 2 | Identify and <b>develop promising demonstration applications</b> to showcase the CXL-based collective communication proposed in OSU's research item 1 |

| ETRI | Goal 1           | Goal 1<br>Single Rack-<br>Scale CXL<br>Memory Pool |   | Proposed Approach 1. CXL SHM-based AllGather                                                                                                          |

|      | Goal 2           | Intelligent CXL<br>Switch                          | 2 | Proposed Approach 2. In-CXL Switch ReduceScatter                                                                                                      |

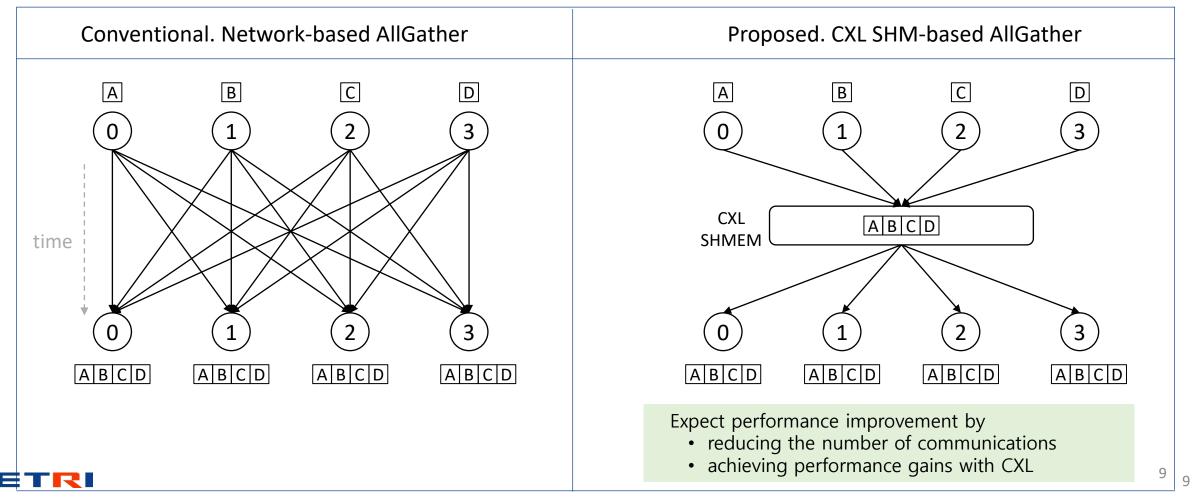

### Proposed Approach for Goal 1

#### CXL SHM-based AllGather

- Design and implement AllGather utilizing the CXL shared memory pool as the collective communication buffer

- Measure Allgather latency with OMB for performance validation

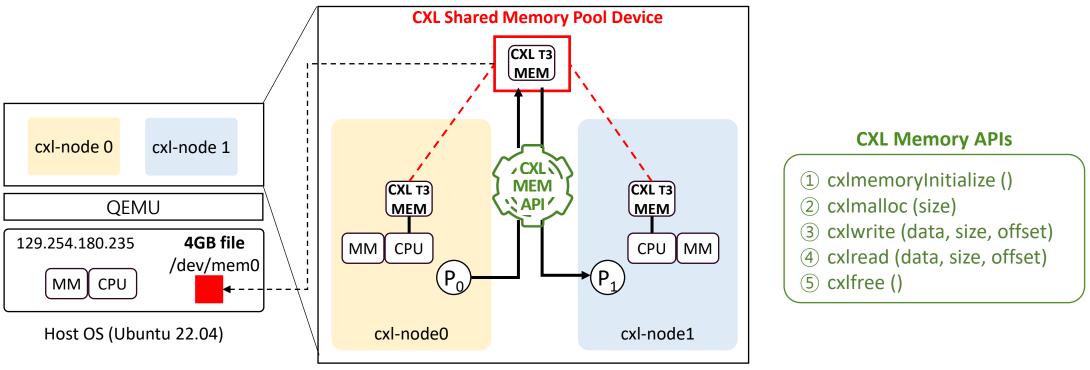

### Implementation for CXL SHM-based AllGather

#### • We developed five CXL memory APIs that are utilized for the CXL SHM-based allgather

MPI ranks running on different computing nodes can utilize the CXL shared memory pool device as the communication buffer for collective communication

**QEMU** Guest OS of Flight Simulator

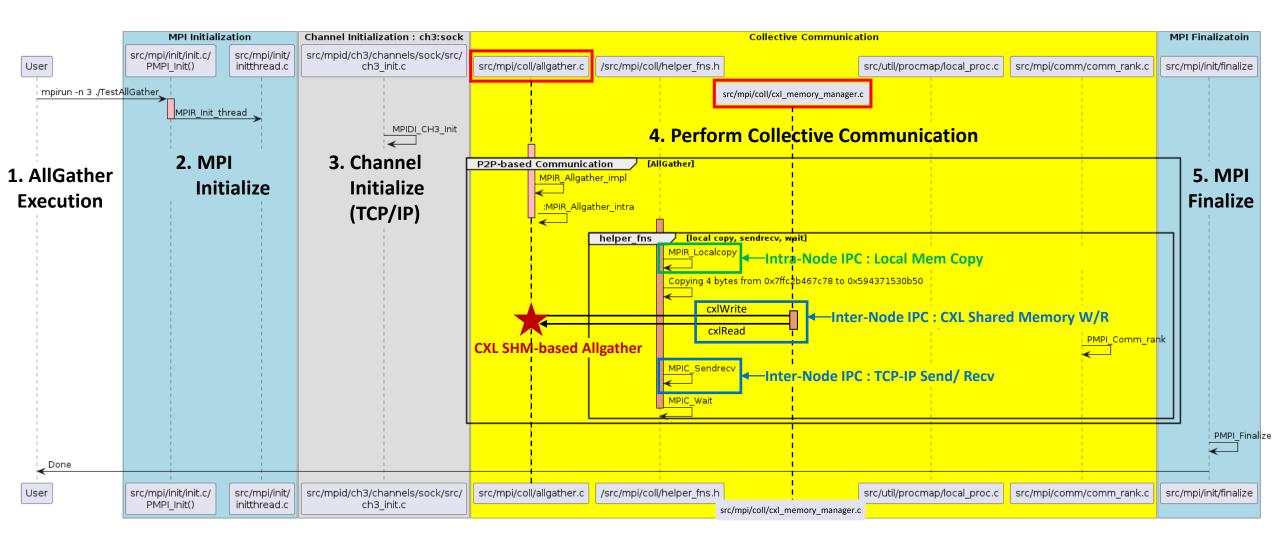

### Implementation for CXL SHM-based AllGather

- We implemented the CXL SHM-based allgather in the allgather.c file of MVAPICH2 2.3.7

- We implemented the cxl\_memory\_manager.c in the coll directory and cxl\_memory\_manager.h in the include directory

### Experimental Setup for CXL SHM-based AllGather

#### Software emulator

• Flight Simulator [5], which emulates the Multi-Node CXL Shared Memory Pool Device in QEMU

### Experimental Environment

- Host Machine

- ✓ CPU : AMD EPYC 9754 128-Core Processor

- ✓ Main memory : 792 GB

- Guest Machine

- ✓ QEMU branch cxl-2024-03-05 [6]

- ✓ OS : fedora release 38 (kernel version : vmlinuz-6.3.7-200.fc38.x86\_64)

### Benchmark Suite

• OSU Micro Benchmarks [7]

### Experimental Items for CXL SHM-based AllGather

|   | Performance metrics to be measured          | Metric (y-axis)      | Variable (x-axis)                  | Fixed Parameters |              |

|---|---------------------------------------------|----------------------|------------------------------------|------------------|--------------|

| 1 | Performance with increasing number of nodes |                      | # of nodes (guest OS)              |                  | PPN          |

|   | renormance with increasing number of nodes  |                      | (e.g., 2, 4, 8, 16)                | 2                | message size |

| 2 | Derformance with increasing DDN             | OMB                  | PPN<br>(e.g., 1, 2, 4, 6)          | 1                | # of nodes   |

|   | Performance with increasing PPN             | AllGather<br>latency |                                    | 2                | message size |

| 3 | Derformance with increasing message size    |                      | message size<br>(e.g., 512KB-32MB) | 1                | # of nodes   |

|   | Performance with increasing message size    |                      |                                    | 2                | PPN          |

☆ PPN (Process Per Node)

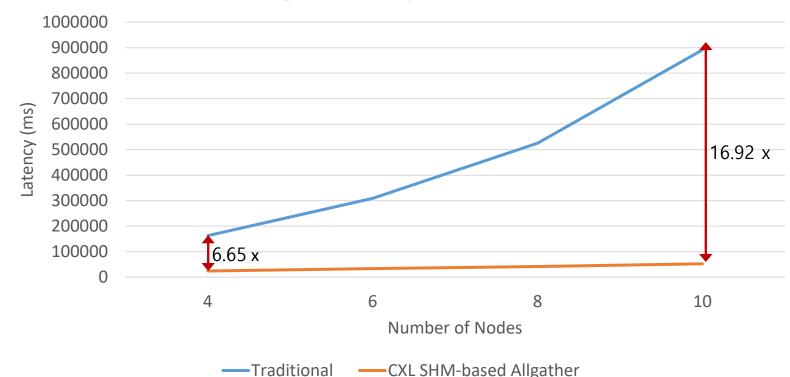

### Experimental Results for CXL SHM-based AllGather

- Performance as the number of nodes increases

- The results showed that with 10 nodes, the maximum performance improvement was 16.92 times

- With 4 nodes, the minimum performance improvement observed was 6.65 times

OMB Allgather Latency (PPN: 4, M: 32MB)

### Experimental Results for CXL SHM-based AllGather

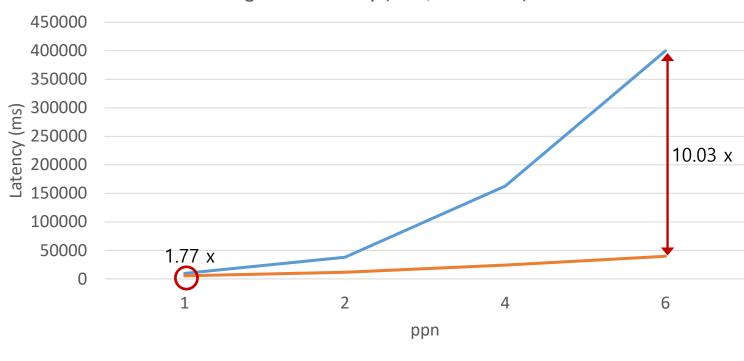

#### Performance as the PPN increases

- The results showed that with 6 PPN, the maximum performance improvement was 10.03 times

- With 1 PPN, the minimum performance improvement observed was 1.77 times

----Traditional

OMB Allgather Latency (N: 4, M: 32MB)

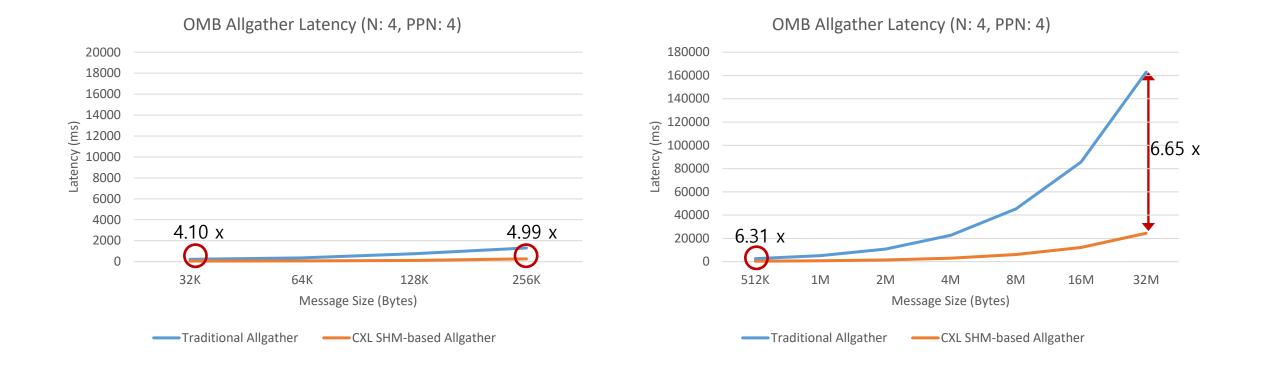

### Experimental Results for CXL SHM-based AllGather

- Performance as the message size increases

- For mid-sized messages, we achieved a maximum performance improvement of 4.99 times

- For large-sized messages, we achieved a maximum performance improvement of 6.65 times

16

### Road Map

We aim to improve the performance of *data-intensive applications* in *multi-node systems*

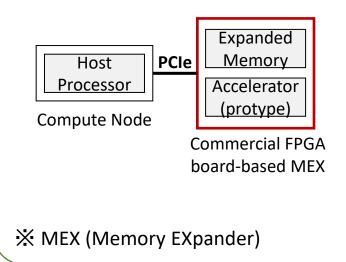

#### Stage 1. MEX

- Commercial FPGA board-based MEX

- Up to 32GB expanded memory

- Prototype version of accelerator

- Support a single node

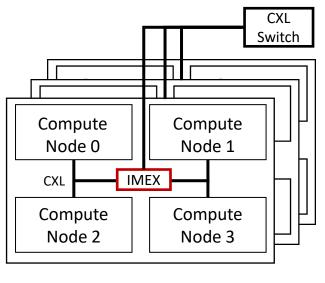

#### Now, we are here Stage 3 Stage 2. iMEX Support multi-node system using CXL Accelerate MPI collective operation using dedicated accelerator to a CXL Switch Use CXL Memory Pool for expanded memory capacity Host **iMEX** Processor Expanded Compute Node 0 CXL Memory Compute Node 0 Accelerator Host CXL Processor Intelligent Compute Compute Node 1 **CXL-Switch** Node 2 based on MEX $\times$ iMEX (intelligent MEX)

- Improvement the scalability of iMEX

- Multiple iMEX devices will be connected

- Support more complex topology

### Conclusion

- We expect to enhance the collective communication performance utilizing iMEX's MPI Computation Accelerator

- We expect to Improve the Memory Utilization for HPC systems utilizing CXL Memory Pool as a MPI Communication buffer

- We expect to Improve the AI and HPC Application performance by reducing the Communication Cost

- We plan to showcase the research progress of iMEX at SC24

### References

- Rajbhandari, Samyam, et al. "Zero-infinity: Breaking the gpu memory wall for extreme scale deep learning." Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis. 2021.

- 2. KLENK, Benjamin, et al. An in-network architecture for accelerating shared-memory multiprocessor collectives. In: 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2020. p. 996-1009.

- 3. Zhou, Qinghua, et al. "Accelerating distributed deep learning training with compression assisted allgather and reduce-scatter communication." 2023 IEEE International Parallel and Distributed Processing Symposium (IPDPS). IEEE, 2023.

- 4. "Enfabrica Scaling CXL Memory Using High Speed Networking ", <u>https://www.youtube.com/watch?v=YdJWhqeT5DM</u>

- 5. "MemVerge Flight simulator, " https://memverge.com/cxl-qemuemulating-cxl-shared-memory-devices-in-qemu/

- 6. "QEMU-CXL branch," https://gitlab.com/jic23/qemu

- 7. "OSU Micro-Benchmarks," <a href="https://mvapich.cse.ohio-state.edu/benchmarks/">https://mvapich.cse.ohio-state.edu/benchmarks/</a>

# Thank You!

Contacts : <u>ahnhy@etri.re.kr</u>